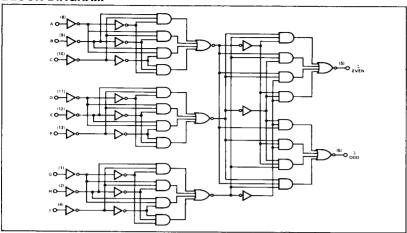

### **BLOCK DIAGRAM**

# 4-BIT BINARY ADDER

54/74283

## SPEED/PACKAGE AVAILABILITY

54LS F,W 74LS B

#### DESCRIPTION

This improved full adder performs the addition of two 4-bit binary numbers. The sum  $(\Sigma)$  outputs are provided for each bit and the resultant carry (C4) is obtained from the fourth bit. This adder features full internal look ahead across all four bits generating the carry term in ten nanoseconds typically. This provides the system designer with partial lookahead performance at the economy and reduced package count of a ripple-carry implementation.

The adder logic, including the carry, is implemented in its true form meaning that the endaround carry can be accomplished without the need for logic or level inversion.

# SWITCHING CHARACTERISTICS $V_{CC} = 5V$ , $T_A = 25$ °C

|                                      | FROM                             | то           |                                | LIMITS |          |          |      |  |

|--------------------------------------|----------------------------------|--------------|--------------------------------|--------|----------|----------|------|--|

| PARAMETER*                           | (INPUT)                          | (OUTPUT)     | TEST CONDITIONS                | MIN    | TYP      | MAX      | UNIT |  |

| <sup>t</sup> PLH<br><sup>t</sup> PHL | C0                               | Any Σ        |                                |        | 16<br>15 | 24<br>24 | ns   |  |

| <sup>t</sup> PLH<br><sup>t</sup> PHL | A <sub>i</sub> or B <sub>i</sub> | $\Sigma_{i}$ | $C_L = 15pF,$ $R_1 = 2k\Omega$ |        | 15<br>15 | 24<br>24 | ns   |  |

| <sup>t</sup> PLH<br><sup>t</sup> PHL | C0                               | C4           | $R_L = 2k\Omega$               |        | 11<br>11 | 17<br>17 | ns   |  |

| <sup>t</sup> PLH<br><sup>t</sup> PHL | A <sub>i</sub> or B <sub>i</sub> | C4           |                                |        | 11<br>12 | 17<br>17 | ns   |  |

<sup>\*</sup>tplH = propagation delay time, low-to-high-level output tpHL = propagation delay time, high-to-low-level output Load circuit and waveforms are shown at the front of the book.

#### PIN CONFIGURATION

| PIN CONFIGURATION |   |                    |  |  |  |  |

|-------------------|---|--------------------|--|--|--|--|

| B,F,W PACKAGE     |   |                    |  |  |  |  |

| Σ2 1              |   | 16 v <sub>cc</sub> |  |  |  |  |

| 82 2              |   | 15 B3              |  |  |  |  |

| A2 3              |   | 14 A3              |  |  |  |  |

| Σ1 4              |   | 13 2 <sub>3</sub>  |  |  |  |  |

| A1 5              |   | 12 A4              |  |  |  |  |

| B1 6              |   | 11 B4              |  |  |  |  |

| C0 7              |   | 10 Σ4              |  |  |  |  |

| GND 8             |   | 9 C4               |  |  |  |  |

|                   | L | l                  |  |  |  |  |

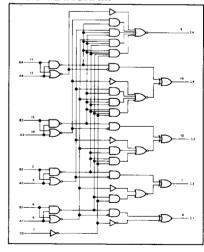

#### **BLOCK DIAGRAM**

/-222

Signetics

#### **TRUTH TABLE**

| ОИТРИТ |           |    |              |    |    |              |    |    |       |

|--------|-----------|----|--------------|----|----|--------------|----|----|-------|

| INPUT  |           |    | WHEN<br>CO=L |    |    | WHEN<br>CO=H |    |    |       |

|        |           |    | WHEN<br>C2=L |    |    | WHEN<br>C2=H |    |    |       |

| A1     | B1        | A2 | B2           | Σ1 | Σ2 | C2           | Σ1 | Σ2 | C2    |

| АЗ     | вз        | A4 | B4           | Σ3 | Σ4 | C4           | Σ3 | Σ4 | C4    |

| L      | L         | L  | ۳            | L  | L  | L            | Н  | L  | L     |

| н      | L         | L  | L            | Н  | L  | L            | L  | н  | L     |

| L      | н         | L  | L            | Н  | L  | Ļ,           | L  | н  | L     |

| Н      | н         | L  | L            | L  | н  | L            | н  | н  | L L L |

| L      | L         | н  | L            | L  | н  | L            | Н  | н  |       |

| H      | L         | Н  | L            | н  | н  | L            | L  | L  | н     |

| L      | н         | н  | L            | н  | н  | L            | L  | L  | Н     |

| н      | Н         | Н  | L            | L  | L  | н            | Н  | L  | н     |

| L      | L         | L  | н            | L  | Н  | L            | Н  | Н  | L     |

| Н      | L         | L  | н            | Н  | н  | L            | L  | L  | Н     |

| L      | н         | L  | н            | н  | Н  | L            | L  | L  | Н     |

| Н      | н         | L  | н            | L  | L  | н            | H  | L  | н     |

| L<br>H | L         | Н  | н            | L  | L  | н            | н  | L  | н     |

| Н      | L         | Н  | н            | н  | L  | н            | L  | н  | Н     |

| L      | Н         | н  | Н            | Н  | L  | н            | L  | н  | H     |

| Н      | <u> H</u> | Н  | H            | L  | Н  | н            | H  | Н. | Н     |

H = high level, L = low level

NOTE: Input conditions at A1, B1, A, B2, and CO are used to determine outputs Σ1 and Σ2 and the value of the internal carry C2. The values at C2, A3, B3, A4, and B4, are then used to determine outputs Σ3, Σ4, and C4.

# DECADE COUNTER

54/74290

## SPEED/PACKAGE AVAILABILITY

54LS F,W 74LS A

#### DESCRIPTION

This monolithic counter contains four master-slave flip-flops and additional gating to provide a divide-by-two counter and a three-stage binary counter for which the count cycle length is divide-by-five.

The 54/74LS290 has a gated zero reset and has gated set-to-nine inputs for use in BCD nine's complement applications.

To use the maximum count length (decade or four-bit binary) of these counters, the B input is connected to the  $Q_A$  output. The input count pulses are applied to input A and the outputs are as described in the function table. A symmetrical divide-by-ten count can be obtained by connecting the  $Q_D$  output to the A input and applying the input count to the B input which gives a divide-by-ten square wave at output  $Q_A$ .

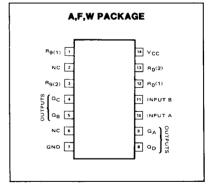

#### **PIN CONFIGURATION**

signetics